#include <OutputChannel.h>

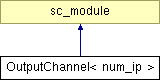

Inheritance diagram for OutputChannel< num_ip >:

Public Member Functions | |

| SC_CTOR (OutputChannel) | |

| Constructor. | |

| void | entry () |

| reads and processes incoming flit | |

| void | closeLogs () |

| void | setTileID (UI tileID, UI portN, UI portS, UI portE, UI portW) |

| sets tile ID and id corresponding to port directions | |

Public Attributes | |

| sc_in< flit > | inport [num_ip] |

| input data/flit ports (one for each IC) | |

| sc_out< bool > | inReady [num_ip] |

| output port to send ready signal to IC | |

| sc_in< bool > | switch_cntrl |

| clock input port | |

| sc_out< flit > | outport |

| output data/flit port | |

| sc_in< creditLine > | credit_in [NUM_VCS] |

| input port to recieve credit info (buffer status) from ICs of neighbor tiles | |

| UI | tileID |

| unique tile ID | |

| UI | cntrlID |

| control ID to identify channel direction (N, S, E, W, C) | |

| UI | portN |

| port number representing North direction | |

| UI | portS |

| port number representing South direction | |

| UI | portE |

| port number representing East direction | |

| UI | portW |

| port number representing West direction | |

| switch_reg | r_in [num_ip] |

| registers to store flit from inport, one for each inport | |

| switch_reg | r_vc [NUM_VCS] |

| registers, one for each next VCID | |

| ULL | latency |

| total latency | |

| ULL | num_pkts |

| total number of packets | |

| ULL | num_flits |

| total number of flits | |

| ULL | input_time |

| generation timestamp of head flit of a packet | |

| float | avg_latency |

| average latency (in clock cycles) per packet | |

| float | avg_latency_flit |

| average latency (in clock cycles) per flit | |

| float | avg_throughput |

| average throughput (in Gbps) | |

| int | beg_cycle |

| clock cycle in which first flit is recieved in the channel | |

| int | end_cycle |

| clock cycle in which last flit leaves the channel | |

| int | total_cycles |

| total number of clock cycles | |

This module defines an Output Channel in a network tile

|

|||||||||

|

closes logfiles at the end of simulation and computes performance stats |

|

|||||||||

|

reads and processes incoming flit Process sensitive to inport event and clock event

|

|

||||||||||

|

Constructor.

|

|

||||||||||||||||||||||||||||

|

sets tile ID and id corresponding to port directions Method to assign tile IDs and port IDs |

|

|||||

|

average latency (in clock cycles) per packet

|

|

|||||

|

average latency (in clock cycles) per flit

|

|

|||||

|

average throughput (in Gbps)

|

|

|||||

|

clock cycle in which first flit is recieved in the channel

|

|

|||||

|

control ID to identify channel direction (N, S, E, W, C)

|

|

|||||

|

input port to recieve credit info (buffer status) from ICs of neighbor tiles

|

|

|||||

|

clock cycle in which last flit leaves the channel

|

|

|||||

|

input data/flit ports (one for each IC)

|

|

|||||

|

generation timestamp of head flit of a packet

|

|

|||||

|

output port to send ready signal to IC

|

|

|||||

|

total latency

|

|

|||||

|

total number of flits

|

|

|||||

|

total number of packets

|

|

|||||

|

output data/flit port

|

|

|||||

|

port number representing East direction

|

|

|||||

|

port number representing North direction

|

|

|||||

|

port number representing South direction

|

|

|||||

|

port number representing West direction

|

|

|||||

|

registers to store flit from inport, one for each inport

|

|

|||||

|

registers, one for each next VCID

|

|

|||||

|

clock input port

|

|

|||||

|

unique tile ID

|

|

|||||

|

total number of clock cycles

|

1.3.9.1

1.3.9.1