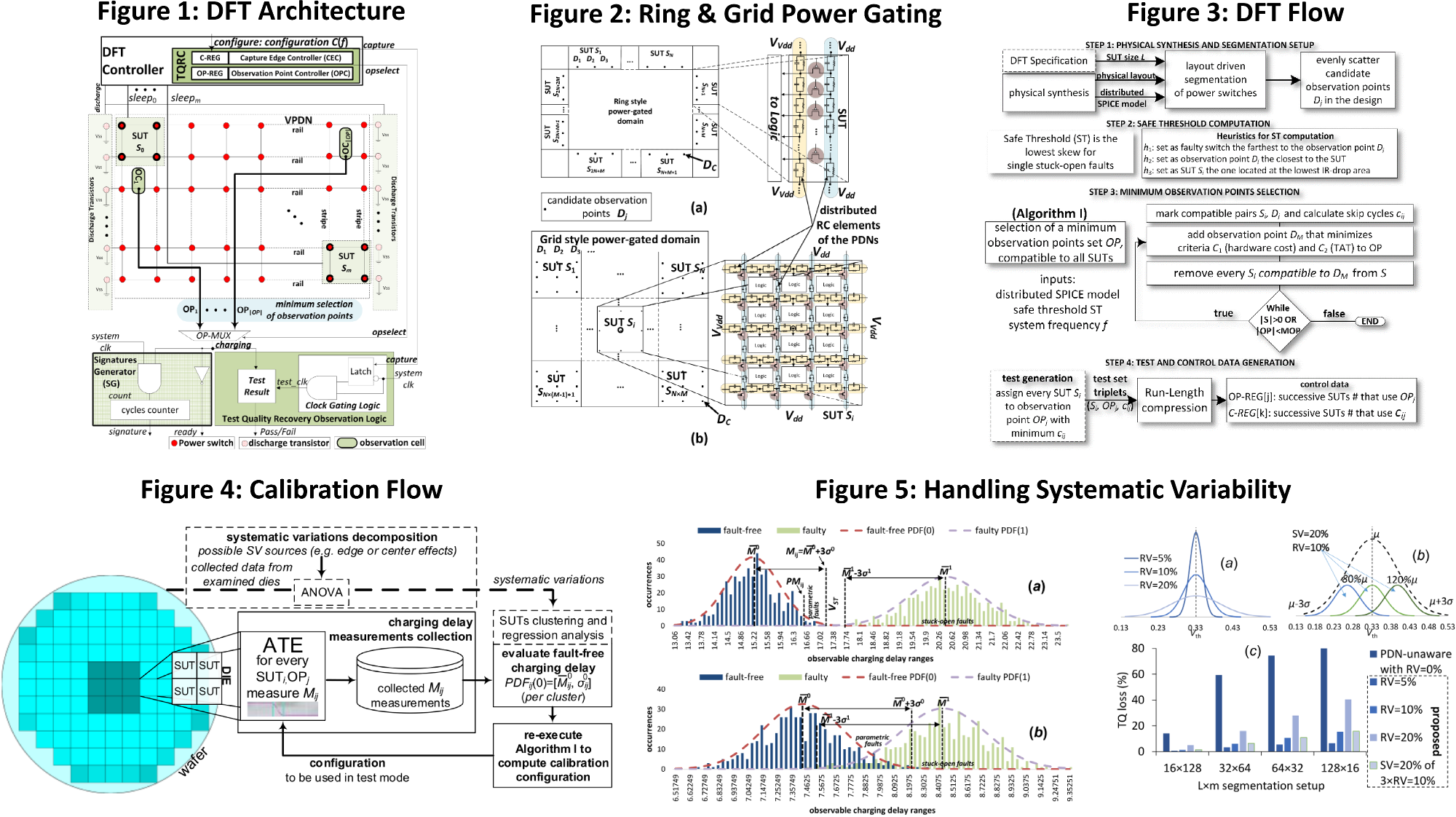

We showed that delay-based testing of power switches must consider a power distribution network (PDN) model in order to avoid fault coverage loss and yield loss. To tackle this problem, we proposed a new PDN-aware DFT architecture (Figure 1), which is suitable for both ring and grid power gating styles (Figure 2). The DFT design flow (Figure 3) consists of practical heuristics for scaling fault simulation requirements and an algorithm that optimizes multiple objectives: test quality, TAT and area cost. The proposed method handles uncertainty and can be calibrated (Figure 4) from post-silicon measurements. An approach to improve test quality when systematic variations are considered was also demonstrated. The simulation results show that the test quality which was lost due to the absence of PDN is now fully recovered and that 83.3% to 98.6% of the restored test quality is robust under process variations (Figure 5). A trade-off between area cost and TAT has also been demonstrated. Finally, the proposed DFT requires minimum area cost of less than 0.42% percent for a design with 157.5K gate.

Publications

V. Tenentes, S. Khursheed, D. Rossi, S. Yang and B. M. Al-Hashimi, "DFT Architecture With Power-Distribution-Network Consideration for Delay-Based Power Gating Test," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 34, no. 12, pp. 2013-2024, Dec. 2015. (doi:10.1109/TCAD.2015.2446939)

V. Tenentes, S. Khursheed, B. M. Al-Hashimi, S. Zhong and S. Yang, "High Quality Testing of Grid Style Power Gating," 2014 IEEE 23rd Asian Test Symposium, Hangzhou, 2014, pp. 186-191. (doi:10.1109/ATS.2014.37)

V. Tenentes, D. Rossi, S. Khursheed and B. M. Al-Hashimi, "Diagnosis of power switches with power-distribution-network consideration," 2015 20th IEEE European Test Symposium (ETS), Cluj-Napoca, 2015, pp. 1-6.