This is a three-year project on "Resilient & Testable Energy-Efficient Digital Hardware" funded by EPSRC UK.

Power management is an essential enabling technology in today’s and future’s low-power devices. The downside of power management is that it decreases the reliability and increase the testability cost of energy-efficient hardware as demonstrated by recent academic and industrial research including that reported by the investigation team. Currently there are no fault models or test methods for power distribution networks and power management circuitry and no on-line soft error monitoring and correction methods for power management hardware. This project is focused on developing new fault models, methods, circuits and their validation (simulation, FPGA and ASIC) to quantify and improve the resilience and testability of energy-efficient digital hardware. Particular emphasis is placed upon cost-effectiveness through joint consideration of reliability, and test and re-using on-chip hardware to minimise silicon area, power consumption and impact on functional performance. This is a three-year project involving two post-doctoral researchers (one for three years and the other for two years), and ARM (Cambridge) as an industrial partner.

| Dr Daniele Rossi, Senior Research Fellow | Dr Vasileios Tenentes, Research Fellow | |

| Dr Saqib Khursheed, Researcher Co-Investigator | Prof. Bashir M. Al-Hashimi, Principal Investigator |

|

Power Gating DFT Architecture

|

Journals

- Tenentes, Vasileios, Rossi, Daniele, K. Chakrabarty, B. M. Al-Hashimi, (2017) Leakage Current Analysis for Diagnosis of Power Gated Designs with Bridge Defect, in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. PP, no. 99, pp. 1-1.

- Daniele Rossi, Vasileios Tenentes, S. M. Reddy and B. M. Al-Hashimi, H. A. Brown, (2017) Exploiting Aging Benefits for the Design of Reliable Drowsy Cache Memories, in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. PP, no. 99, pp. 1-1.

- D. Gutierrez, Mauricio Tenentes, Vasileios, D. Rossi, Kazmierski, Tom J., (2017) Susceptible Workload Evaluation and Protection using Selective Fault Tolerance, in Journal of Electronic Testing, Springer.

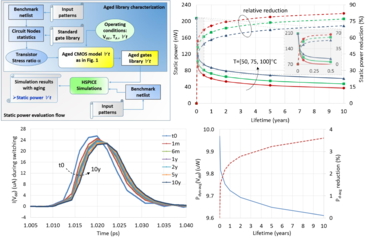

- Rossi, Daniele, Tenentes, Vasileios, Yang, Sheng, Khursheed, Saqib and Al-Hashimi, Bashir (2016) Aging benefits in nanometer CMOS designs. IEEE Transactions on Circuits and Systems II Express Briefs, doi: 10.1109/TCSII.2016.2561206.

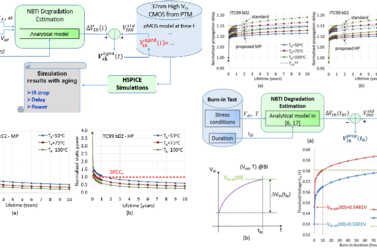

- Tenentes, Vasileios, Rossi, Daniele, Yang, Sheng, Khursheed, Saqib, Al-Hashimi, Bashir M. and Gunn, Steve R. (2016) Coarse-grained Online Monitoring of BTI Aging by Reusing Power Gating Infrastructure. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, accepted.

- Halak, Basel, Tenentes, Vasileios, Rossi, Daniele, (2016) The impact of BTI aging on the reliability of level shifters in nano-scale CMOS technology, Microelectronics Reliability, Elsevier,\\doi:10.1016/j.microrel.2016.10.018, early access.

- Rossi, Daniele, Tenentes, Vasileios, Yang, Sheng, Khursheed, Saqib and Al-Hashimi, Bashir (2015) Reliable power gating with NBTI aging benefits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 24, no. 8, pp. 2735-2744.

- Tenentes, Vasileios, Khursheed, Saqib, Rossi, Daniele, Yang, Sheng and Al-Hashimi, Bashir M. (2015) DFT architecture with power-distribution-network consideration for delay-based power gating test. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 34, no. 12, pp. 2013-2024.

Conferences

- Tenentes, Vasileios, Leech, Charles, Bragg, Graeme, Merrett, Geoffrey, Al-Hashimi, Bashir, Amrouch, Hussam, Henkel, Jörg and Das, Shidhartha (2017) Hardware and software innovations in energy-efficient system-reliability monitoring In IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems. IEEE. 5 pp.

- Gutierrez Alcala, Mauricio, Daniel, Tenentes, Vasileios, Kazmierski, Tomasz and Rossi, Daniele (2017) Low cost error monitoring for improved maintainability of IoT applications At IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems. 23 - 25 Oct 2017. 6 pp.

- D. Gutierrez, Mauricio, Tenentes, Vasileios, Rossi, Daniele, Kazmierski, Tom J., Concurrent Detection of Systematic Errors for Low Power Non-safety Critical Applications, submitted to 22nd IEEE European Test Symposium (ETS), 2017

- Chahal, Hardeep, Tenentes, Vasileios, Rossi, Daniele and Al-Hashimi, Bashir M. (2016) BTI aware thermal management for reliable DVFS designs. In, Defect and Fault Tolerance in VLSI and Nanotechnology Systems Symposium (DFT'16), Connecticut, US, 19 - 20 Sep 2016. 6pp. (best paper award nominee)

- D. Gutierrez, Mauricio, Tenentes, Vasileios, Kazmierski, Tom J., (2016) Susceptible Workload driven Selective Fault Tolerance using a Probabilistic Fault Model, accepted at, 22nd IEEE International On-Line Testing Symposium, Spain, 04 - 06 Jul 2016. 6pp.

- Rossi, Daniele, Tenentes, Vasileios, Khursheed, Saqib and Al-Hashimi, Bashir M. (2015) BTI and leakage aware dynamic voltage scaling for reliable low power cache memories. In, 21st IEEE International On-Line Testing Symposium, Halkidiki, Greece, 06 - 08 Jul 2015. 6pp.

- Tenentes, Vasileios, Rossi, Daniele, Khursheed, Saqib and Al-Hashimi, Bashir M. (2015) Diagnosis of power switches with power-distribution-network consideration. In, 20th IEEE European Test Symposium (ETS 2015), Cluj-Napoca, RO, 25 - 29 May 2015. 6pp.

- Rossi, Daniele, Tenentes, Vasileios, Khursheed, Saqib and Al-Hashimi, Bashir (2015) NBTI and leakage aware sleep transistor design for reliable and energy efficient power gating. In, IEEE European Test Symposium 2015, Cluj-Napoca, RO, 25 - 29 May 2015. 6pp.

- Tenentes, Vasileios, Khursheed, Syed Saqib, Al-Hashimi, Bashir M., Zhong, Shida and Yang, Sheng (2014) High quality testing of grid style power gating. In, 23rd Asian Test Symposium (ATS), Hangzhou, CN, 16 - 19 Nov 2014. 6pp.