#include <NWTile.h>

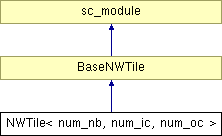

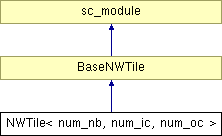

Inheritance diagram for NWTile< num_nb, num_ic, num_oc >:

Public Member Functions | |

| SC_HAS_PROCESS (NWTile) | |

| Constructor. | |

| NWTile (sc_module_name NWTile, UI tileID) | |

| void | entry () |

| Writes buffer utilization information at the tile, at each clock cycle. | |

| void | setID (UI) |

| sets unique tile id and associates ports with directions | |

| void | closeLogs () |

| closes log files at the end of simulation | |

| float | return_latency (int port_dir) |

| returns average latency per packet for a channel | |

| float | return_latency_flit (int port_dir) |

| returns average latency per flit for a channel | |

| float | return_avg_tput (int port_dir) |

| returns average throughput for a channel | |

| int | return_total_latency () |

| returns total latency across all channels in the tile | |

| int | return_total_flits () |

| returns total flits across all channels in the tile | |

| int | getportid (int port_dir) |

| returns id corresponding to a port direction (N, S, E, W) | |

| SC_HAS_PROCESS (BaseNWTile) | |

Public Attributes | |

| sc_in< bool > | switch_cntrl |

| input clock port | |

| sc_in< flit > | ip_port [num_nb] |

| input data/flit ports | |

| sc_out< flit > | op_port [num_nb] |

| output data/flit ports | |

| sc_in< creditLine > | credit_in [num_nb][NUM_VCS] |

| input ports for credit line (buffer status) | |

| sc_out< creditLine > | credit_out [num_nb][NUM_VCS] |

| output ports for credit line (buffer status) | |

| InputChannel< num_oc > * | Ichannel [num_ic] |

| Input channels. | |

| OutputChannel< num_ic > * | Ochannel [num_oc] |

| Output channels. | |

| VCAllocator< num_ic > | vcAlloc |

| Virtual Channel Allocator. | |

| ipcore * | ip |

| IP Core. | |

| Controller< num_ic > | ctr |

| Controller. | |

| sc_signal< flit > | flit_sig [num_ic][num_oc] |

| signals to connect data outport of ICs to the data inport of the OCs | |

| sc_signal< flit > | flit_CS_IC |

| data line from ipcore to input channel | |

| sc_signal< flit > | flit_OC_CR |

| data line from output channel to ipcore | |

| sc_signal< bool > | rdy [num_ic][num_oc] |

| ready signals from ICs to OCs of neighboring tiles | |

| sc_signal< bool > | vcReq [num_ic] |

| Request signal for virtual channel allocation from IC to VCA. | |

| sc_signal< sc_uint< 2 > > | opReq [num_ic] |

| Output port requested from IC to VCA. | |

| sc_signal< bool > | vcReady [num_ic] |

| Ready signal from VCA to IC. | |

| sc_signal< sc_uint< VCS_BITSIZE+1 > > | nextvc [num_ic] |

| Virtual channel id allocated from VCA to IC. | |

| sc_signal< creditLine > | creditIC_CS [NUM_VCS] |

| credit line from core channel to VCA and ipcore | |

| sc_signal< request_type > | rtReq [num_ic] |

| Routing request signal from IC to Ctr. | |

| sc_signal< sc_uint< ADDR_SIZE > > | destReq [num_ic] |

| Destination address from IC to Ctr. | |

| sc_signal< sc_uint< ADDR_SIZE > > | srcAddr [num_ic] |

| Source address from IC to Ctr. | |

| sc_signal< bool > | rtReady [num_ic] |

| Ready signal from Ctr to IC. | |

| sc_signal< sc_uint< 3 > > | nextRt [num_ic] |

| Route (output port) signal from Ctr to IC. | |

| UI | tileID |

| unique tile id | |

| UI | portN |

| port representing North direction | |

| UI | portS |

| port representing South direction | |

| UI | portE |

| port representing East direction | |

| UI | portW |

| port representing West direction | |

This module defines a network tile and submodules within it. It is derived from abstract class BaseNWTile. Template parameters:

|

||||||||||||||||

|

Constructor to create a network tile. Creates and connects the following submodules:

|

|

|||||||||

|

closes log files at the end of simulation Closes log files at the end of simulation |

|

|||||||||

|

Writes buffer utilization information at the tile, at each clock cycle. Process sensitive to clock. Writes buffer utilization info at each clock |

|

||||||||||

|

returns id corresponding to a port direction (N, S, E, W) Returns id corresponding to a given port direction (N, S, E, W) |

|

||||||||||

|

returns average throughput for a channel Returns average throughput across a given channel Implements BaseNWTile. |

|

||||||||||

|

returns average latency per packet for a channel Returns average latency per packet across a given channel Implements BaseNWTile. |

|

||||||||||

|

returns average latency per flit for a channel Returns average latency per flit across a given channel Implements BaseNWTile. |

|

|||||||||

|

returns total flits across all channels in the tile Returns total number of flits across all channels in the tile Implements BaseNWTile. |

|

|||||||||

|

returns total latency across all channels in the tile Returns total latency across all channels in the tile Implements BaseNWTile. |

|

|

systemC constructor parameters - module name, tile id. |

|

||||||||||

|

Constructor.

|

|

||||||||||

|

sets unique tile id and associates ports with directions

|

|

|||||

|

input ports for credit line (buffer status)

|

|

|||||

|

output ports for credit line (buffer status)

|

|

|||||

|

credit line from core channel to VCA and ipcore

|

|

|||||

|

|

|

|||||

|

Destination address from IC to Ctr.

|

|

|||||

|

data line from ipcore to input channel

|

|

|||||

|

data line from output channel to ipcore

|

|

|||||

|

signals to connect data outport of ICs to the data inport of the OCs

|

|

|||||

|

Input channels.

|

|

|||||

|

IP Core.

|

|

|||||

|

input data/flit ports

|

|

|||||

|

Route (output port) signal from Ctr to IC.

|

|

|||||

|

Virtual channel id allocated from VCA to IC.

|

|

|||||

|

Output channels.

|

|

|||||

|

output data/flit ports

|

|

|||||

|

Output port requested from IC to VCA.

|

|

|

port representing East direction

|

|

|

port representing North direction

|

|

|

port representing South direction

|

|

|

port representing West direction

|

|

|||||

|

ready signals from ICs to OCs of neighboring tiles

|

|

|||||

|

Ready signal from Ctr to IC.

|

|

|||||

|

Routing request signal from IC to Ctr.

|

|

|||||

|

Source address from IC to Ctr.

|

|

|||||

|

input clock port

|

|

|

unique tile id

|

|

|||||

|

Virtual Channel Allocator.

|

|

|||||

|

Ready signal from VCA to IC.

|

|

|||||

|

Request signal for virtual channel allocation from IC to VCA.

|

1.3.9.1

1.3.9.1